Abstract

Systems and methods for teaching a location in a device programming apparatus. The X, Y, Z and angle coordinates of a pick and place nozzle are initialized, and the nozzle is moved in the X and Y coordinates to a position above the device in the location to be taught. The new X and Y coordinates of the nozzle are stored to a memory along with the initial angle coordinate. The system automatically determines the Z location of the surface of the device. The nozzle then automatically picks up the device and performs vision centering to determine the X, Y and angle offsets with respect to the initialized coordinates. The X, Y and angle offsets are used to modify the stored X, Y and angle coordinates so as to precisely determine the X and Y location of the device center as well as the device angle with respect to the system’s global reference frame.

Description

CROSS REFERENCES TO RELATED APPLICATIONS

This application is related to U.S. Provisional Patent Application Ser. No. 60/117,873, filed Jan. 29, 1999, entitled “IN-LINE PROGRAMMING DEVICE WITH SELF-TEACHING CAPABILITY,” and U.S. Provisional Patent Application Ser. No. 60/122,023, filed Feb. 26, 1999, entitled “PICK AND PLACE TEACHING METHOD AND APPARATUS FOR IMPLEMENTING THE SAME,” the disclosures of which are each hereby incorporated by reference in its entirety.

BACKGROUND OF THE INVENTION

The present invention generally relates to automatic configuration of semiconductor device handling equipment to accommodate multiple applications and random variations among machines and devices.

In the semiconductor industry, a considerable number of electronic devices are provided by vendors in programmable form with blank memories or unspecified connections between arrays of logic. Users can then custom configure or program the electronic devices to perform their intended function by programming them, transferring or “burning in” a sequence of operating codes into the memory, or by specifying a particular arrangement of gating logic connections.

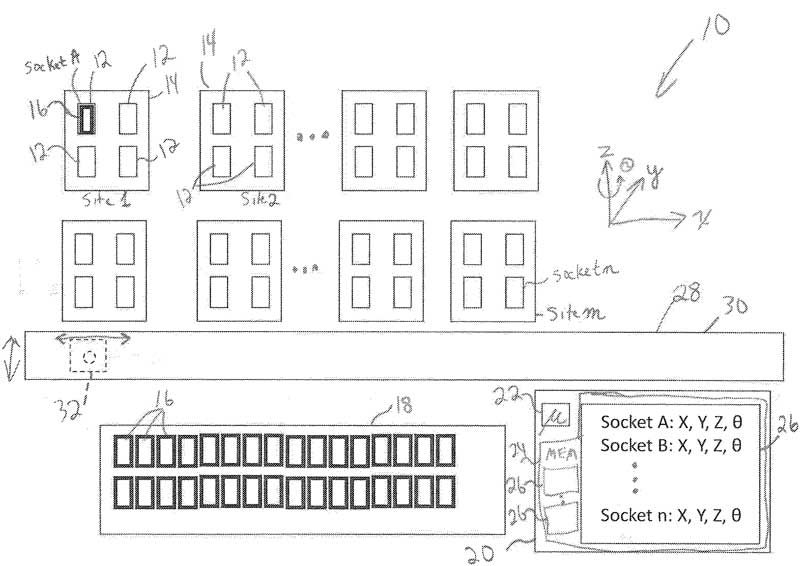

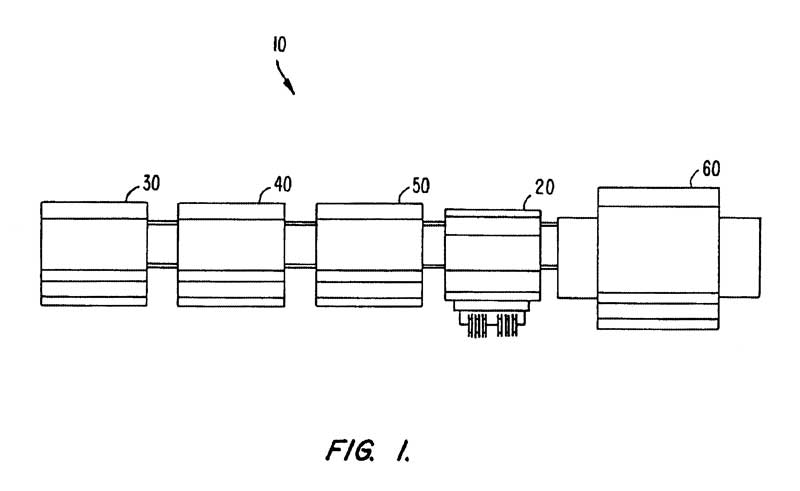

Numerous manufacturers have developed automated machinery for handling and programming such devices. Such machinery moves blank devices from a source medium (e.g., trays, tubes, etc.) to one or more programming sites, carries out the programming operation on each device, and moves programmed devices from the programming sites to an output medium (e.g., trays, tubes, etc.).

Both to allow flexible handling of a wide variety of automated programming operations (different types of input or output media, different device package types, etc.) and to account for inevitable manufacturing variations from machine to machine, it is necessary for the equipment operator to configure (or “teach”) the automated programming machinery the precise locations from which to pick up devices and to which to place devices. This includes all input and output media locations, the locations of all programming site sockets, and any other such locations within the system.

Accurate teaching is critical to the robust operation of automated programming systems. While older, larger programmable devices are relatively insensitive to placement accuracy, modem fine pitch devices have very delicate leads and suffer damage unless placement operations are highly accurate (for instance, correct to within 0.001″).

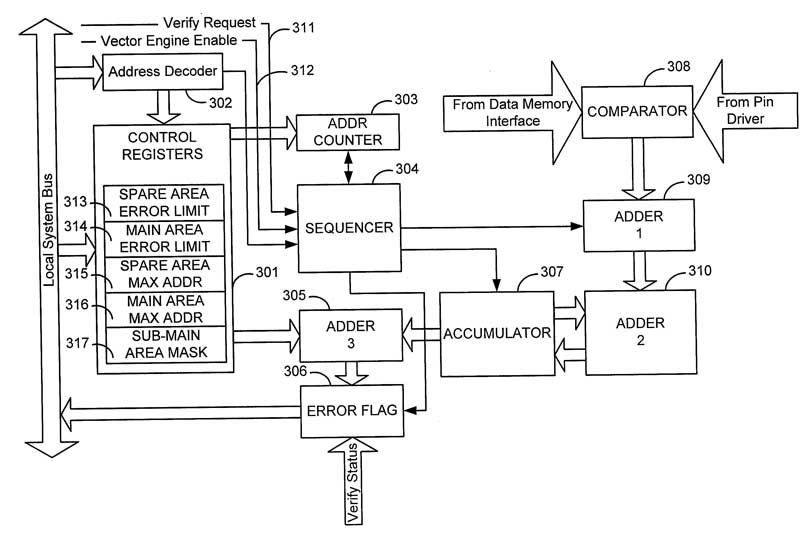

Not all automated equipment can achieve such accurate placement. In order to do so, high-end equipment uses a technique known as vision centering. The system picks up each device with a pick and place nozzle and holds the device in the path of a series of parallel laser beams. The device is then rotated in the path of the laser beams. A bank of sensors monitors which of the beams is interrupted during the rotation of the device. This information can be processed numerically to identify the precise angle and position of the device on the pick and place nozzle. Linear encoder technology allows the system to place the nozzle at any desired location. The results of the vision centering operation allow a correction move in the lateral horizontal (i.e., X, Y) and angle coordinates to be performed so that the part can be precisely placed at the desired location.

Traditional vision centering does not assist the user in determining the correct pick and place locations. Rather, it merely enables the system to place with extreme accuracy once those locations are specified.

While the ease with which the operator can carry out the teaching operation does not directly affect the physical treatment of devices, it does affect the efficiency of system operation. Typical users of automated programming equipment are highly sensitive to system throughput (measured in correctly programmed devices per hour) and yield (defined as the percentage of devices which are correctly programmed). Furthermore, more difficult teaching techniques require more highly trained personnel that draw higher wages. As a result of all of these considerations, automated programming equipment users prefer fast, easy teaching techniques.

A variety of teaching techniques has been implemented to date. These include none, file-controlled, trial-and-error, single point downward vision teaching, and double point downward vision teaching. Each of these techniques is characterized by advantages and disadvantages when considered in terms of accuracy and ease of use.

Some equipment requires no teaching whatsoever. This equipment is simple to set up and use, but is limited to devices that are rugged and can tolerate the relatively imprecise component placement that results from inevitable manufacturing variations from machine to machine. Such equipment is normally also limited to a specific device type or a small range of types and offers little flexibility to handle new devices.

Some equipment requires no active teaching on the part of the user, but offers improved flexibility by utilizing CAD data files to determine the location of device pick and place points. Systems of this type offer more flexible handling of a variety of jobs, but are still limited to rugged components that can tolerate relatively poor placement accuracy, because this teaching technique doesn’t account for random manufacturing variations.

A wide variety of equipment is available that provides operator control over the various pick and place locations but offers no systematic technique to help the operator determine the proper settings. The operator of such equipment must pursue a trial-and-error approach until correct settings are determined. Once accurately configured, such equipment can operate very reliably, but the trial-and-error process can be very time consuming and can result in many damaged (and hence unusable) parts. Equipment of this type still normally handles only rugged devices.

Some automated device programming systems are equipped with downward vision cameras. Such a camera is mounted to the movable portion of the system and can be positioned over any point in the system workspace. The camera can “look down” on the components or component locations. The operator can observe the camera field of view on a monitor which is normally equipped with crosshairs for precise positioning. Downward vision cameras can be used in “single point” or “double point” teaching mode.

In a system that employs single point downward vision teaching, the operator positions the camera crosshairs over the estimated center of the component location to be taught and indicates via a keystroke, mouse click, or some other event that the proper position has been identified. The system then stores this position and returns to it when necessary. This approach provides better accuracy than all previously described techniques, and requires only a single camera positioning operation by the user. However, the approach requires that the operator visually estimate the proper crosshair location. This can be inaccurate unless the location being taught exhibits some kind of distinct “landmark” at the center point, which is not always the case. When such a landmark is available, systems of this type can properly handle delicate fine pitch parts, while some device damage can result in the absence of such landmarks.

Double point downward vision teaching improves upon the single point technique by allowing the user to teach two points and taking as the teach point the arithmetic average of those two points. In most systems it’s much easier to find two symmetrically located “landmarks” than to find a single landmark at the precise target location. A disadvantage of this approach, however, is that the operator must position the crosshairs twice, doubling the labor involved in the teaching process. Historically, double point downward vision teaching has provided the most reliable results and has proven most successful in handling fine pitch devices.

None of the approaches described above fully exploit the fine positioning capability of modem motion control equipment. Even the most accurate of the above methods, double point downward vision teaching, requires that the operator visually align two references (the camera crosshair and the image landmark) with one another. Human vision is not capable of performing this feat to the full accuracy of motion control hardware. The approaches that do work well require extensive operator involvement and thus admit the possibility of human error.

A much more serious limitation of all existing approaches is that none of them deal effectively with angular and vertical axis coordinates. All of the approaches described above address only the lateral horizontal components of the device location. In the above approaches, angular error is normally neglected, and the vertical coordinate must be set by the operator using visual inspection of the proximity of the pick and place nozzle to the top of the device.

SUMMARY OF THE INVENTION

Briefly, the present invention provides a new and improved technique for teaching automated programming equipment that exploits the full accuracy of the system’s pick and place capabilities while requiring minimal effort on the operator’s part. The approach requires that the operator place a device in the location to be taught. The system then picks the device up, performs vision centering measurements on the device, and uses the results of these measurements to determine the precise place coordinates for the device. This information is stored in the system in a manner that prevents the need to perform teaching for any given combination of hardware items more than once.

The teaching process begins automatically when the system, e.g., via software, recognizes that the target coordinates associated with an imminent placement have not been initialized. The system guides the operator through the steps required to determine the proper values for all four coordinates (X, Y, Z, and angle).

First, the system displays an alert box on the computer monitor identifying the location in question and instructing the user to place a device in the location. Some locations (e.g., programming site sockets) hold the device in a very well defined position. Others (e.g., device pockets in input and output media) may allow a degree of play in the device’s location. After the user has placed a device in the location, he or she must ensure that the system nozzle is roughly over the device. This subjective specification of a position by the operator does not affect the final coordinates determined by the teach process. The operator must merely be close enough to allow the system to pick the part up. When the operator is satisfied with the rough location, he or she notifies the system software to indicate permission to move to the next step.

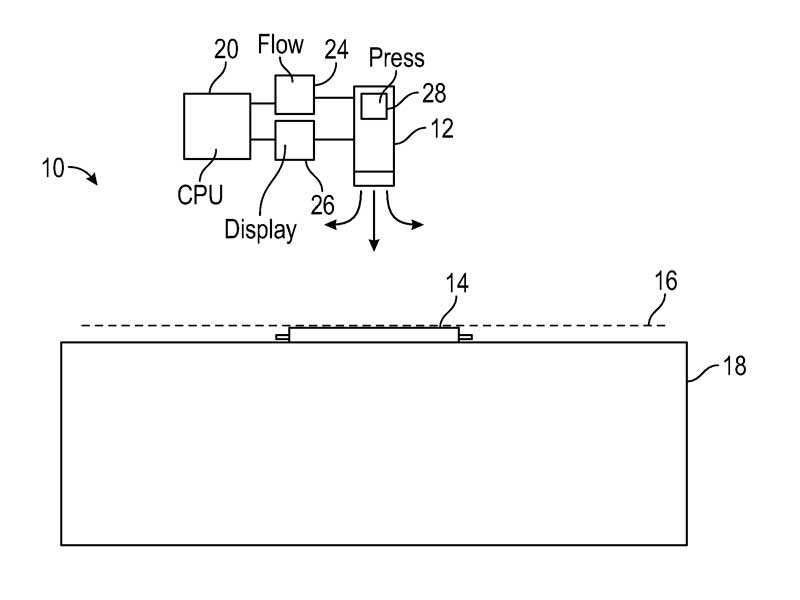

Once the operator indicates that the vacuum nozzle is over the device, the system software takes over and begins to step the nozzle downward toward the device’s upper surface. After each step the system uses a proximity sensor to determine whether the nozzle is in contact with the device. As long as the nozzle has not made contact with the device, the downward stepping process continues. Once contact is established, this part of the teaching process is complete and the vertical position of the nozzle is stored as the Z coordinate associated with the teach process for this particular location and device.

Once the Z coordinate is established, the system is capable of picking the device from its location. In one embodiment, a vacuum nozzle is used. The device is picked up by activating the vacuum nozzle while the nozzle is in contact with the device.

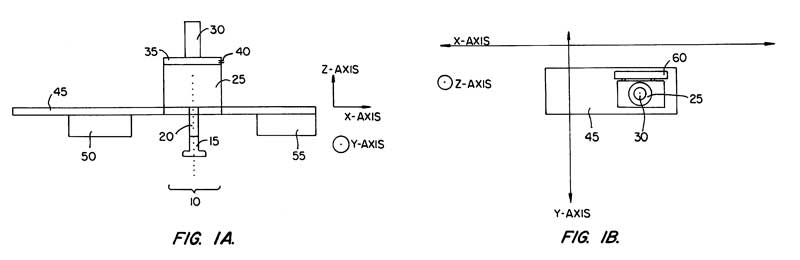

The system software continues the teaching process by positioning the device in the laser align beam(s) and using the vision centering process to determine the precise X, Y, and angle offsets with respect to the nozzle. The software is also able to determine the nozzle X and Y coordinates (relative to initialized X and Y axes) using linear encoder feedback. By suitably combining the encoder readings with the laser align measurement results, the system software determines the precise X and Y location of the device center as well as the device angle with respect to the system’s global reference frame. When the measurement process is complete, the system places the device back in its original position.

According to an aspect of the invention, a method is provided for teaching a location in a device programming apparatus. The method typically comprises the steps of providing a device in the location to be taught, providing a nozzle capable of picking up the device, wherein the nozzle has an initial set of horizontal coordinates and an initial vertical coordinate, and positioning the nozzle to a first set of horizontal coordinates different from the initial set of horizontal coordinates such that the nozzle is above the device. The method also typically comprises the steps of automatically determining, with the nozzle, the vertical position of the device relative to the initial vertical coordinate, automatically determining, for each of the horizontal coordinates, offset coordinates of the center of the device relative to the nozzle, and combining the horizontal offset coordinates with the first set of horizontal coordinates so as to determine the location of the device relative to the initial set of coordinates.

According to another aspect of the invention, a method is provided for teaching a location in a device programming apparatus. The method typically comprises the steps of providing a device in the location to be taught, wherein the device has an associated identifier, determining whether teaching data associated with the identifier is stored in a memory; and if not, providing a nozzle capable of picking up the device, wherein the nozzle has an initial set of horizontal coordinates and an initial vertical coordinate, and positioning the nozzle to a first set of horizontal coordinates different from the initial set of horizontal coordinates such that the nozzle is above the device. The method also typically comprises the steps of automatically determining, with the nozzle, the vertical position of the device relative to the initial vertical coordinate, automatically determining, for each of the horizontal coordinates, offset coordinates of the center of the device relative to the nozzle, combining the horizontal offset coordinates with the first set of horizontal coordinates to produce teaching data that identifies the location of the device relative to the initial set of coordinates, and storing the teaching data to the memory in association with the device identifier.

According to yet another aspect of the invention, a device programming apparatus with self-teaching capability is provided. The apparatus typically comprises a nozzle assembly having a nozzle capable of picking up a device in a location to be taught, wherein the center of the nozzle has an initial set of horizontal coordinates and an initial vertical coordinate, and a means for positioning the nozzle to a first set of horizontal coordinates different from the initial set of horizontal coordinates such that the nozzle is above the device. The apparatus also typically comprises a means for automatically determining, with the nozzle, the vertical position of the device relative to the initial vertical coordinate, a means for automatically determining, for each of the horizontal coordinates, offset coordinates of the center of the device relative to the center of the nozzle, and a means for modifying the first set of horizontal coordinates with the horizontal offset coordinates so as to produce teaching data that identifies the location of the device relative to the initial set of coordinates.

According to a further aspect of the invention, a method is provided for teaching a location in a device programming apparatus. The method typically comprises the steps of providing a device in the location to be taught, providing a nozzle capable of picking up the device, wherein the nozzle has an initial set of coordinates defined by three orthogonal axes and an initial angle coordinate defined by a first and a second one of the three axes, and positioning the nozzle to a first set of coordinates such that the nozzle is proximal the device, wherein the first set of coordinates is different from the initial coordinates along the first and second axes. The method also typically comprises the steps of automatically determining, with the nozzle, the position of the device along the third axis relative to the initial third axis coordinate, automatically determining offset coordinates of the center of the device relative to the nozzle for each of the first and second axes coordinates and the angle coordinate, and combining the offset coordinates with the first set of coordinates and the initial angle coordinate so as to determine the location and orientation of the device relative to the initial set of coordinates and initial angle coordinate.

Reference to the remaining portions of the specification, including the drawings and claims, will realize other features and advantages of the present invention.

Further features and advantages of the present invention, as well as the structure and operation of various embodiments of the present invention, are described in detail below with respect to the accompanying drawings. In the drawings, like reference numbers indicate identical or functionally similar elements.