US Patent: Electronic apparatus and bit error rate tolerance method for programming non-volatile memory devices

US Patent 2009/0287969

Inventors: Brandon L. White, Danny Tjandra

Abstract

The present invention provides an apparatus and method for using a bit error rate tolerance (BERT) technique for high-speed programming of non-volatile electronic memory devices. The device programmer is comprised of an embedded computer system and specialized electronic circuitry to interface to the device to be programmed. According to one aspect of the invention, the device programmer contains digital registers to accumulate the number of incorrect data bits encountered during the verification of the device programming operation. A field-programmable input to the device programmer specifies the BERT to be allowed at precise intervals within the device. Devices that are found to exceed the specified BERT shall be rejected.

Description

This application claims priority from U.S. Provisional Patent Application No. 61/052,889, filed May 13, 2008, entitled “ELECTRONIC APPARATUS AND BIT ERROR RATE TOLERANCE METHOD FOR PROGRAMMING NON-VOLATILE MEMORY DEVICES.” This application is hereby incorporated by reference in its entirety for all purposes.

BACKGROUND OF THE INVENTION

1. Field of Invention

The present invention relates to the field of automated transfer of electronic data into non-volatile digital memory devices. In particular, the present invention relates to electronic systems and methods for the detection of erroneous data occurring in such devices during data transfer.

2. Description of the Related Art

In the electronics manufacturing industry, it is often desirable to transfer data into a non-volatile semiconductor device, such as flash memory, using special-purpose programming machines known as device programmers. Employing device programmers to handle this task is often necessary to achieve an initial state in the device such that it may then be assembled into a larger electronic system, known as an embedded system. This pre-programming of an initial state allows the manufactured system to achieve basic functionality for further programming of the device by other means, usually as a function of the manufactured embedded system itself. This practice may also extend to other areas related to electronics manufacturing that include, but are not limited to, research and development, and failure analysis.

It is often practical to utilize the device programmer to pre-program all intended data into the device during manufacture as a cost reduction technique. Embedded systems may have particular design attributes such as low power consumption combined with reduced performance processing units that achieve less than maximal data transfer rates of the memory device. Device programmers can often achieve much more rapid transfer times which can increase the rate of system manufacture thereby lowering the per-unit manufacturing cost.

Certain types of modern, large capacity, non-volatile memory devices, such as NAND Flash, exhibit reliability errors in the data stored in the device. These errors manifest as output data that contains unpredictable differences from the original input data. The frequency of these errors increases with the repeated erasure and programming of the cells internal to the device. It is a burden of the system that interfaces to the flash device to detect and correct such errors, where possible.

To improve the accuracy of the data transferred out of a non-volatile memory device, e.g., a flash device, to a level acceptable by the application of the system, error correction code (ECC) algorithms are widely used. Such algorithms compute code values in relation to the data to be stored in the device. These code values are typically stored in the flash device itself along with the original data. Upon transfer of data output from the flash device, the code data is output as additional information. The system receiving the data from the flash device makes use of a decoding algorithm that utilizes the code to detect, and in most cases correct, incorrect binary data states in the received transfer.

A limitless number of practical implementations of ECC techniques exist. There are various encoding and decoding algorithms, and each can be varied in numerous ways to suit particular requirements as will be understood to those skilled in the art. The frequency and manner in which the code values are arranged in relation to the original data present yet another vast mixture of possibilities. Additionally, some systems are known to combine multiple ECC implementation techniques in a dynamic hybrid fashion (see, e.g., US Pat. App. Pub. No. 20040083333A1, which is hereby incorporated by reference).

ECC algorithms are designed in a manner such that the decoding operation indicates the number of individual bit errors present in the data transferred from the device, if any. Furthermore, an additional computation can then be performed in the event of such bit errors so as to correct these errors. Generally, ECC algorithms can correct some lesser number of errors than can be detected. For instance, a 4-bit ECC algorithm may be able to detect the presence of 5 or more invalid bits in a block of data, but is only capable of precisely identifying and thus correcting 4 of the erroneous bits. The integrity of the embedded system can be maintained so long as the bit error rate (BER) for any block of data transferred from the flash memory device does not exceed the correction limits of the ECC algorithm used to encode that data block.

ECC algorithms require complex computations and as such incur latencies when the system accesses the data in the device. Generally, the stronger the ECC algorithm in terms of the number of bit correction ability, the more computational overhead is required. ECC algorithms may be implemented as software instructions for a processing unit, or may be implemented in whole or in part on dedicated hardware logic circuitry to increase the performance of the computations.

When pre-programming a NAND flash device by way of a device programming machine, data corruption failures must be detected. If these failures exceed the limits of the target embedded system’s ECC algorithm correction capability, then the device must be rejected and excluded from further assembly into the target system circuit.

In the prior art, device programmers leveraged the assumption that NAND flash devices would not yield bit errors during manufacturing pre-programming due to the lack of disturbance issues in new devices. While this certainly remains true for Single Level Cell (SLC) NAND flash devices, Multiple Level Cell (MLC) devices can and will in fact experience program disturbance issues on the first and subsequent program operations that will lead to incorrect bit states upon transfer of the data from the device.

Applying conventional device programmer methods to MLC NAND flash devices results in unsuccessful yield, as nearly all devices would be rejected by the machine upon detection of the erroneous data bits in the output.

Implementing the ECC algorithm used by the embedded system in the device programmer is an obvious but inadequate solution. The computational overhead for these algorithms is not suitable for the rates desired for electronics manufacturing. Furthermore, the exact details of any particular embedded system’s ECC methods might be difficult or impossible to obtain. Advanced ECC methods are often proprietary, with multiple parties involved and the license for such use untenable. Lastly, the cost to develop such algorithms on a per-device, per-system basis is typically prohibitive.

Therefore, a need exists for a device programming machine with an improved method and apparatus for data verification within a bit error rate tolerance threshold. That is, what is desired is a method and apparatus for high-speed pre-programming of MLC NAND Flash or other non-volatile memory devices within the capabilities of any arbitrary ECC algorithm without employing such algorithms directly.

BRIEF SUMMARY

Briefly, the present invention provides an apparatus and method for using a bit error rate tolerance (BERT) technique for high-speed programming of non-volatile electronic memory devices. The device programmer, in certain aspects, includes an embedded computer system and specialized electronic circuitry to interface to the device to be programmed.

According to one embodiment, a method for using a bit error rate tolerance technique during high-speed programming of non-volatile memory devices is disclosed. The method comprises receiving a tolerance value representing a maximum number of bit errors that a memory region in a non-volatile memory device can tolerate. Next, the method analyzes a memory region of the non-volatile memory device to find the number of bit errors contained in the memory region of the device without running an error correcting code algorithm. The method then compares the number of bit errors found in the analyzed memory region of the non-volatile memory device to the tolerance value. Non-volatile memory devices in which the number of bit errors found in the analyzed memory region of the non-volatile memory device is greater than the tolerance value are then rejected.

According to another embodiment, a device programmer apparatus for programming a non-volatile memory device is disclosed. The apparatus comprises a means for storing data to be transferred into memory of a non-volatile memory device, a means for transferring data into memory of the non-volatile memory device, a means for analyzing a memory region of the non-volatile memory device that stores the transferred data to find the number of bit errors contained in the memory region without running an error correcting code algorithm, a means for comparing the number of bit errors found in the analyzed memory region of the non-volatile memory device to a tolerance value representing a maximum number of bit errors that a memory region in the memory device can tolerate, and a means for rejecting the non-volatile memory device if the number of bit errors found in the analyzed memory region of the non-volatile memory device is greater than the tolerance value.

According to another embodiment, a computer readable medium with computer-executable code is disclosed. The computer-readable medium comprises code for receiving a tolerance value representing a maximum number of bit errors that a memory region in a non-volatile memory device can tolerate, code for analyzing a memory region of the non-volatile memory device to find the number of bit errors contained in the memory region of the device without running an error correcting code algorithm, code for comparing the number of bit errors found in the analyzed memory region of the non-volatile memory device to the tolerance value, and code for rejecting the non-volatile memory device if the number of bit errors found in the analyzed memory region of the non-volatile memory device is greater than the tolerance value.

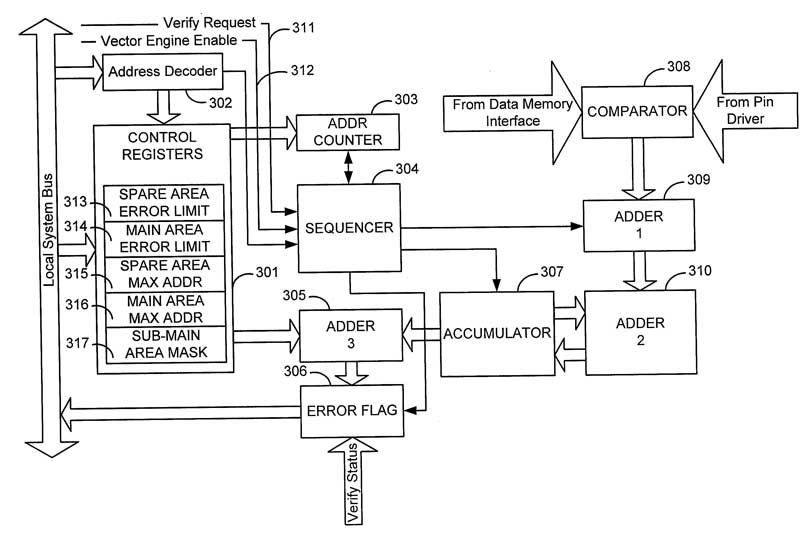

According to another embodiment of the invention, a device programmer contains digital registers to accumulate the number of incorrect data bits encountered during the verification of the device programming operation. A field-programmable input to the device programmer specifies a bit error rate tolerance (BERT) to be allowed at precise intervals within the device. Devices that are found to exceed the specified BERT can be rejected and visually indicated as such by the machine.

According to another embodiment of the present invention, a BERT input is set according to the ECC capabilities of the target system into which the device will be assembled. A device programmer will only indicate successful programming status for devices that contain a number of bit errors equal to or less than the correction capabilities of the target system’s ECC algorithm. Devices failing to meet this specification can be rejected and visually indicated as such by the machine to prevent further assembly of the device into the target system, thereby avoiding the assembly of a non-functional target system.

In another embodiment, an apparatus includes the circuitry and implements simultaneous programming of multiple quantities of devices. Each device’s error statistics are computed and retained discretely by the device programmer circuitry in real-time, as is necessary to manage the random distribution of possible error bits on individual devices.

According to still another aspect of the present invention, multiple BERT inputs may be specified by the operator of the device programmer, as desired, to accommodate varying tolerances for different memory regions of the memory device.

Further aspects and advantages of the present invention shall become apparent upon reading and understanding the following detailed descriptions of example embodiments and studying the various figures of the drawings.